A variety of applications require tasks to be programmed sequentially and continually iterate on these tasks. Most notably are telecommunications applications require simultaneous transmit and receive. In the following example, a simple telecommunications example illustrates how these sequential tasks can be pipelined to leverage multicore environments.

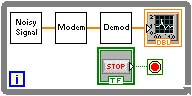

Consider the following simple modulation -demodulation example where a noisy signal is modulated transmitted and demodulated. A typical diagram is shown in Figure Sequential Tasks.

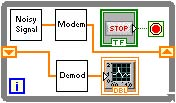

Adding a shift register to the loop allows tasks to be pipelined and be executed in parallel in separate cores should they be available. Task pipelining is shown in Figure Pipelined Tasks.

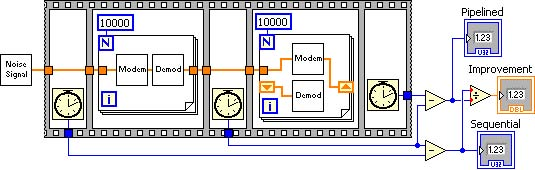

The program below times the sequential task and the pipelined tasks to establish its performance improvement when executed in multicore computers.

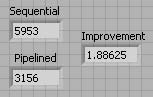

Figure Pipelining Performance Improvement shows the results of running the above G program in a dual core 1.8 GHz laptop. Pipelining shows nearly 2x performance improvement.

- 1812 reads